-

Tips for becoming a good boxer - November 6, 2020

-

7 expert tips for making your hens night a memorable one - November 6, 2020

-

5 reasons to host your Christmas party on a cruise boat - November 6, 2020

-

What to do when you’re charged with a crime - November 6, 2020

-

Should you get one or multiple dogs? Here’s all you need to know - November 3, 2020

-

A Guide: How to Build Your Very Own Magic Mirror - February 14, 2019

-

Our Top Inspirational Baseball Stars - November 24, 2018

-

Five Tech Tools That Will Help You Turn Your Blog into a Business - November 24, 2018

-

How to Indulge on Vacation without Expanding Your Waist - November 9, 2018

-

5 Strategies for Businesses to Appeal to Today’s Increasingly Mobile-Crazed Customers - November 9, 2018

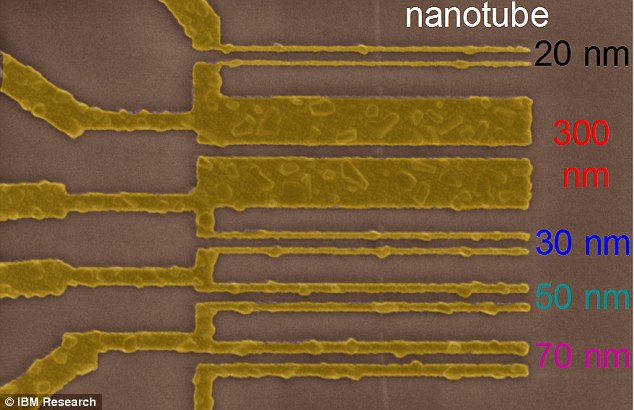

IBM Says Its Carbon&Nanotube&Based Chips Can Break Through Limits of Moore’s Law

Carbon Nanotube Valley doesn’t have the same ring to it as Silicon Valley, but we might have to live with it, if IBM’s newest breakthrough has legs.

Advertisement

IBM scientists demonstrated a new way to shrink transistor contacts without reducing performance of carbon nanotube devices, opening a pathway to dramatically faster, smaller and more powerful computer chips beyond the capabilities of traditional semiconductors.

Earlier this summer, IBM unveiled the first 7-nanometer node silicon test chip, pushing the limits of silicon technologies.

“These chip innovations are necessary to meet the emerging demands of cloud computing, Internet of Things and Big Data systems”, said Dario Gil, vice president of Science & Technology at IBM Research. The chips could be smaller and faster and significantly surpass what’s possible with today’s silicon semiconductors. Better transistors can offer higher speed while consume less power.As part of the world’s long search for technologies that can stave off The End of Moore’s Law, and carbon nano-tech is a multi-billion dollar research effort in IBM alone.

We’ve discussed the difficulties of scaling semiconductors as the distance between features shrinks with every passing generation, but the specific breakthrough IBM is claiming is in an area of chip design we haven’t discussed much.

IBM said that as devices get smaller, increased electrical resistance has prevented serious performance gains.

The company notes that scaling carbon nanotube-based transistors to smaller sizes is limited by two things: the size of the device’s channel and the size of its contacts. Simply decreasing the size of the contact hasn’t worked. The breakthrough, revealed on Thursday, describes a way of bonding molybdenum to a carbon nanotube in order to create a contact point for a circuit.

Schematics showing the conversion from a side-bonded contact (left), where the SWNT is partially covered by Mo, to end-bonded contact (right), where the SWNT is attached to the bulk Mo electrode through carbide bonds while the carbon atoms from originally covered portion of the SWNT uniformly diffuse out into the Mo electrode.

Carbon nanotubes, though, require materials to be laid down on the chip with extraordinary precision. By making contacts in this fashion, the scale of the transistor can be reduced without also increasing resistance at the contacts. For carbonnanotubes, many material issues have to be solved to obtain similar high-quality carbon nanotube wafers for device fabrication. IBM has built functional silicon-germanium transistors at 7 nanometres, but say that this pushes the limits of what the can be done with the material, while Intel has stated that it won’t be using silicon beyond the 10nm scale – current Intel CPUs are at 14nm, and the next generation will be 10nm. The IBM research result show that that contacts less than 10 nanometers long don’t compromise performance, and could be extended down to 1.8 nanometer.

Advertisement

“Our novel approach is to make the contact from the end of the carbon nanotube, which we show does not degrade device performance”. They now sit between 11 and 14 nanometres, and anything closer to that would increase resistance to the point where the chip would start losing on performance.